## Unidirectional High-Frequency-Link DC to Three-Phase AC Conversion: Topology, Modulation and Converter Design

A Thesis Submitted For the Degree of **Doctor of Philosophy** In the Faculty of Engineering

> by Anirban Pal

Department of Electrical Engineering **INDIAN INSTITUTE OF SCIENCE** Bangalore – 560 012 December 2019

## Dedication

This thesis is dedicated to my parents, uncle and aunt for their endless love, support and encouragement to follow my dreams.  $This \ page \ is \ intentionally \ left \ blank$

## Acknowledgements

I want to express my sincere gratitude to my adviser, Dr. Kaushik Basu, who has been an excellent mentor for me. He has shaped my understanding of various concepts of Power Electronics. He has given me the freedom to think independently and to explore new ideas. His inputs in writing technical manuscripts have improved my skill in conveying technical ideas lucidly. His constant encouragement and inspiration to work hard have helped me immensely during the difficult times of this journey. As I am his first Ph.D. student, we both started our journey together. His vision for setting up our laboratory, development of controller and power hardware have helped to complete my work within the stipulated time frame. His advice on both research and my career has been priceless.

I would like to thank Prof. G. Narayanan, who was my ME adviser, for his support and encouragement. Under his guidance, I got hands-on experience in building the power converter during my ME days. This experience has motivated me further to work on converters in my Ph.D. I am grateful to Prof. V. John who has helped me with thought-provoking questions, which have improved my understanding of the area. My sincere thanks to him to have made funds available for building the hardware. I thank all the professors in IISc who have taught me different subjects and have helped to improve my understanding of various concepts.

I thank our EE office staff, Mr. Channe Gowda, Mr. Purushottam, Mr. Kini, Venkatamma and Rudresh for being helpful with all administrative works. I thank Mr. Erwine Paul for his help regarding any projector related issues faced during my presentations in MMCR.

I gratefully acknowledge MHRD, Govt. of India for the financial support during this period and DST-SERB, Govt. of India, for supporting my travel to attend the ECCE conference.

I am thankful to my seniors Anil Adapa, D. Venkatramanan, Abhijit K, Shahjahan and others for their valuable inputs on different aspects of Power Electronics. I express my heartfelt gratitude to Bala and Sayan who has helped me immensely to set up the lab and to build the hardware during the initial stage of my Ph.D. I am grateful to my friends and PEG lab mates specially Sayan, Dibakar, Shamibrota, Shimul, Sugoto, and Anwesha Di for their help, support, and constant encouragement. We used to have wonderful technical and non-technical discussions from where I have learned a lot many things. I would like to thank my juniors Soham, Rahul, Mihir, Deekshith, Manmohan, Sushmit, Shubhangi, Sheenu, Prachin, Manish, Aditya, Hari and others for always being supportive and for making the lab a lively place to work in. I must thank my junior Kapil, for giving me insightful suggestions which have improved my understanding of the work. I thank my lab mate Vishal for being helpful and supportive in different technical and non-technical aspects of life. I especially thank my friend Srinivas Gulur, who motivated me to continue for Ph.D after completion ME here. The life outside the lab was very vibrant. I cherish the wonderful time I have had with my B-mess friends Rupam, Arpita, Niladri, Sayak, Sayantan, Pubali, Pritha, Rudrashis, Sanjay, Rownik, Shubham, who have brightened every dull meal of the mess with their jokes, fun, and laughter. You are my support system for which I never felt the fatigue of the work and could continue here without losing motivation. This long journey would not have been fun without you.

I cherish my days as a student of Nihar Da, who introduced me to the world of notes, tunes, and rhythms. He is my violin guru. In this regard, I am grateful to my friend Dibakar, who himself is an excellent violin player. He first encouraged me to listen to western classical music and then took me to Nihar Da. Playing the violin is a wonderful experience in my life and would have been completely unexplored without his encouragement.

Lastly, I thank my parents, my uncle, and aunt for their constant encouragement that has been vital during my Ph.D. I would not have reached here without their patience and support along the way.

Anirban Pal

## Abstract

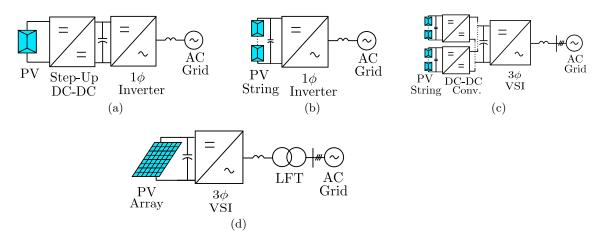

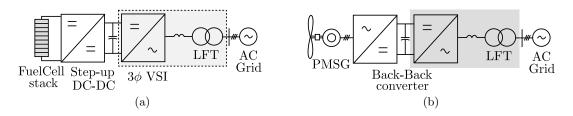

In recent years, stringent restrictions on greenhouse gas emission due to the present global warming scenario is driving governments and power utilities worldwide behind electricity generation using renewable energy sources. Conventionally, for grid integration of a large scale photovoltaic (PV) system, a three-phase voltage source inverter followed by a line frequency transformer (LFT) is used. The inverter generates line frequency (50/60 Hz) AC from the DC output of PV. The LFT provides galvanic isolation and thus reduces the circulation of leakage current, and ensures safety. Few limitations with the conventional system are a) huge volume as the LFT is bulky, (b) quite expensive due to large amount of iron and copper used in LFT and (c) the inverter is hard switched. The converter topologies with high-frequency galvanic isolation have attractive features like high power density and are less expensive. Hence these converters are promising alternatives to the conventional solution.

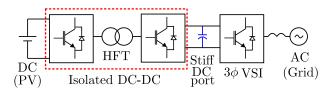

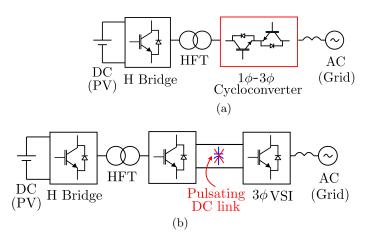

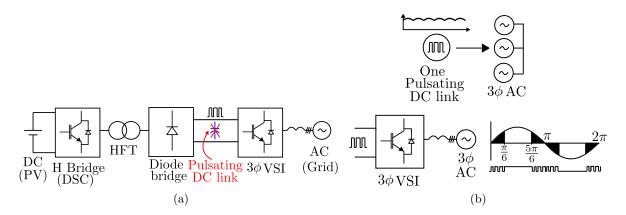

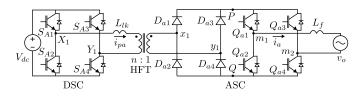

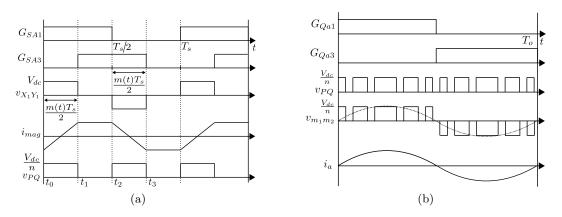

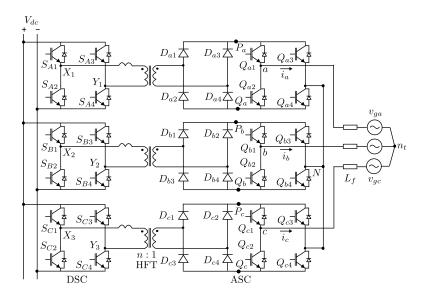

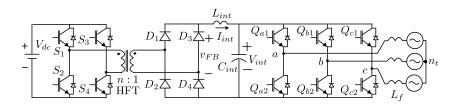

The three-phase inverter topologies with high-frequency transformer are generally of two types- a) multi-stage and b) single-stage. In multi-stage, interstage DC link is voltage stiff as filter capacitor is used. In a single-stage solution, the intermediate DC link is pulsating as filter capacitor is avoided to improve reliability. Though these converters have high power density, they employ large number of active switches on both the sides of the transformer to process power and hence have relatively lower efficiency compared to the conventional solution. The active switch count can be reduced in case of unidirectional applications like grid integration of PV, fuel-cell where the active power flows from DC source to AC grid. The converter efficiency can be further improved by reducing the switching loss. In this work, we have investigated four new unidirectional single-stage three-phase inverter topologies with low or negligible switching loss.

To reduce the switching loss, the active switches of the introduced topologies are either line frequency switched or high-frequency soft-switched. The soft-switching is achieved without additional snubber circuit. The pulse width modulation is implemented on the input DC side converters which are soft-switched. The active switches of the grid interfaced converter are low frequency switched and thus enabling the use of high voltage blocking inherently slow semiconductor devices for direct medium voltage grid integration. The topologies are gradually improved to achieve soft-switching of the DC side converters throughout the line cycle. The conditions on dead time to ensure soft-switching are derived through detailed circuit analysis. The operations of these topologies are experimentally verified on hardware prototypes with power range 2-6kW. Out of four introduced topologies, three topologies can support only unity power factor operation. An additional shunt compensator is needed for any reactive power support. The fourth topology can support up to  $\pm 0.866$  power factor operation though it has relatively higher conduction loss. The performances of the introduced topologies are compared with multi-stage and conventional solutions. Though the new topologies have relatively higher switch counts, the converter power losses, filter requirements are comparable with the conventional solution with line frequency transformer, and have high power density.

## Contents

| Ac | cknov                                                                       | ledgements                                                                                                                                                                                                                                                                                                                                                                         | i                                                    |  |  |  |

|----|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|

| Ał | Abstract iii                                                                |                                                                                                                                                                                                                                                                                                                                                                                    |                                                      |  |  |  |

| Li | st of                                                                       | Tables                                                                                                                                                                                                                                                                                                                                                                             | ix                                                   |  |  |  |

| Li | st of                                                                       | Figures                                                                                                                                                                                                                                                                                                                                                                            | xv                                                   |  |  |  |

| Ac | crony                                                                       | ns                                                                                                                                                                                                                                                                                                                                                                                 | xvii                                                 |  |  |  |

| No | omen                                                                        | lature                                                                                                                                                                                                                                                                                                                                                                             | xix                                                  |  |  |  |

| 1  | 1.1<br>1.2<br>1.3                                                           | duction         Background and Motivation         Grid integration of photovoltaics: State-of-the-art         High-frequency-link based solutions         High-frequency-link based solutions         1.3.1         Multi-stage high frequency link inverter         1.3.2         Single-stage high frequency link inverter         Unidirectional RHFL DC-3 $\phi$ AC converters | · 2<br>· 4<br>· 4<br>· 5<br>· 6                      |  |  |  |

|    | $1.5 \\ 1.6 \\ 1.7$                                                         | Aim of the work                                                                                                                                                                                                                                                                                                                                                                    | . 7                                                  |  |  |  |

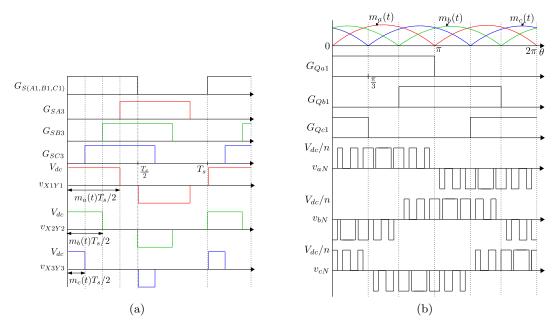

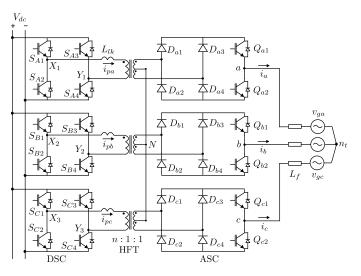

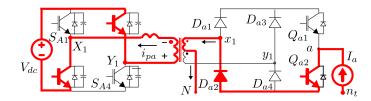

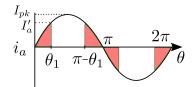

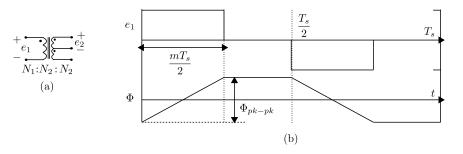

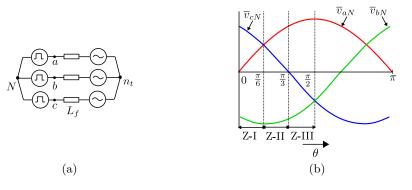

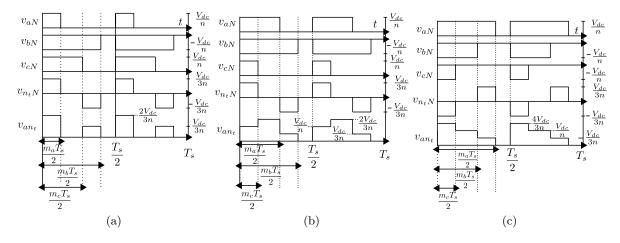

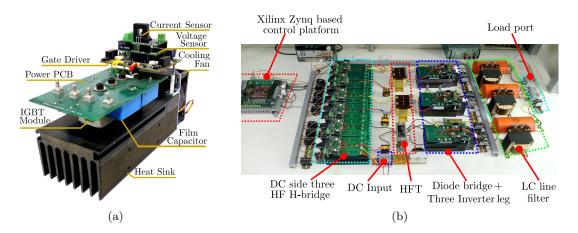

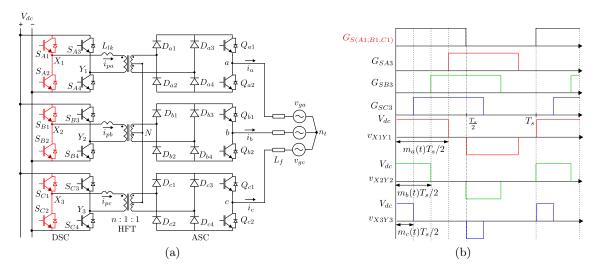

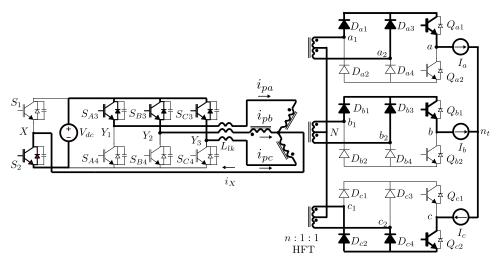

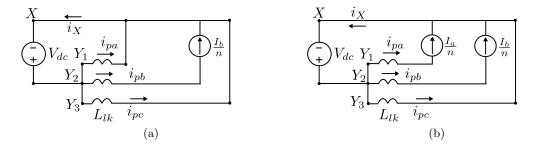

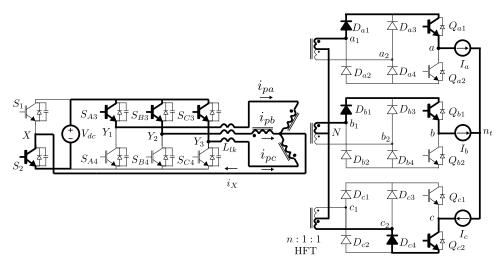

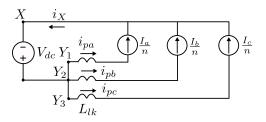

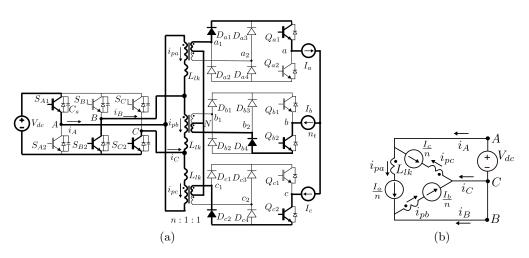

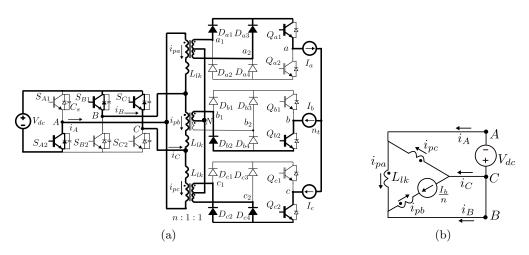

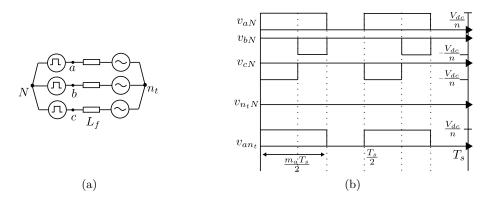

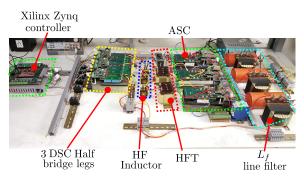

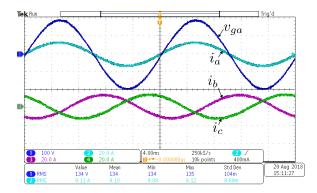

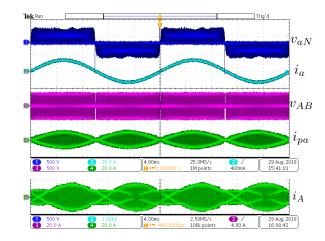

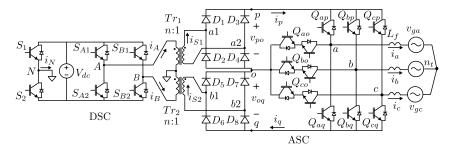

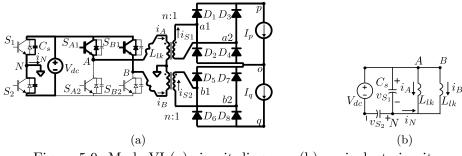

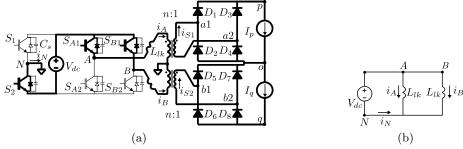

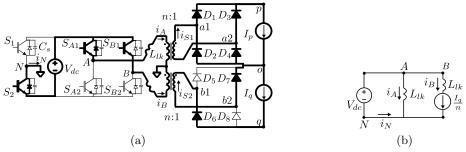

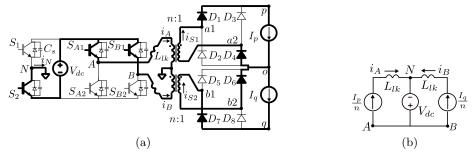

| 2  | <ul> <li>Uni</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> </ul> | irectional HFL DC-3 $\phi$ AC with 3 pulsating DC links: Topology-1<br>Introduction                                                                                                                                                                                                                                                                                                | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |  |  |

|    | 2.5                                                                         | 2.4.4Input and Output Filter Requirement of the ConverterExperimental Results                                                                                                                                                                                                                                                                                                      | . 32<br>. 34                                         |  |  |  |

|   |              | 2.5.3 Estimation of circuit parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|---|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

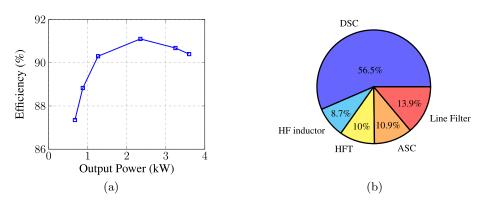

|   |              | 2.5.4 Measurement of converter power loss and efficiency $\ldots \ldots \ldots \ldots \ldots 40$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

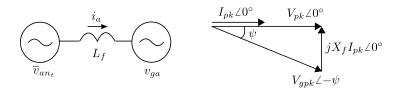

|   | 2.6          | Compensation of line filter drop and reactive power support 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|   | 2.7          | Conclusion $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

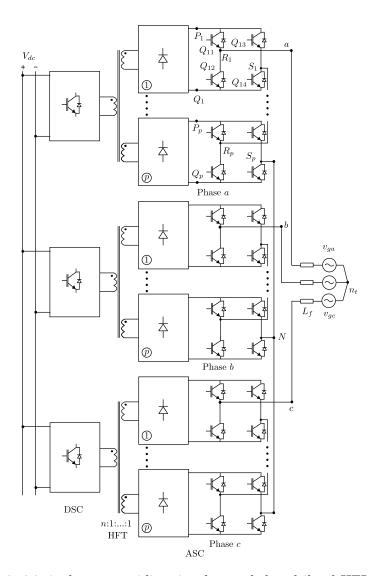

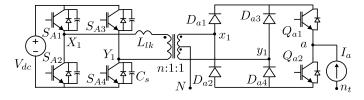

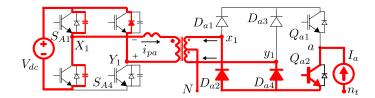

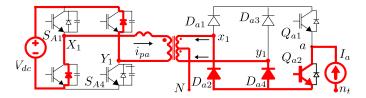

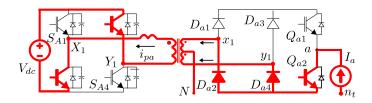

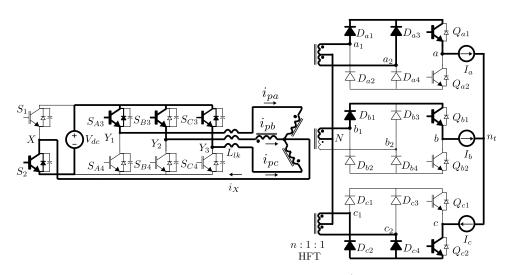

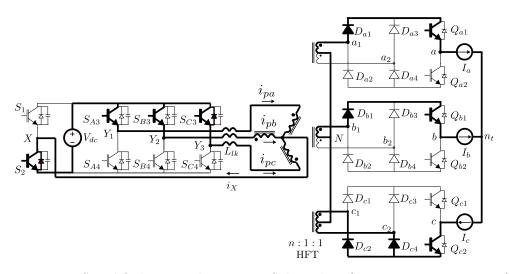

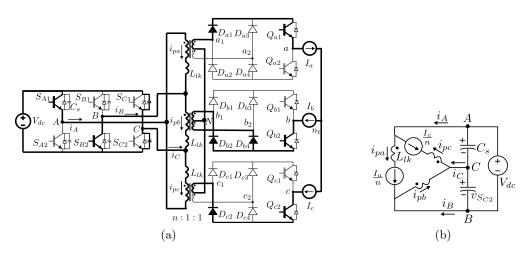

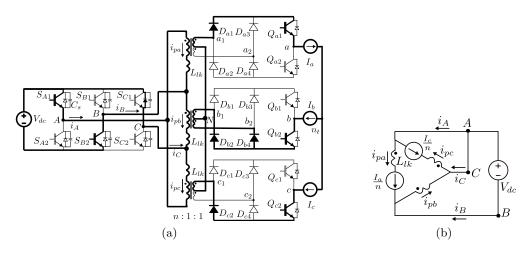

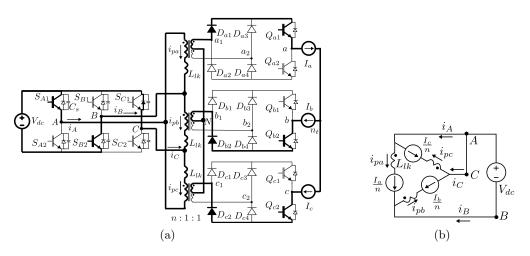

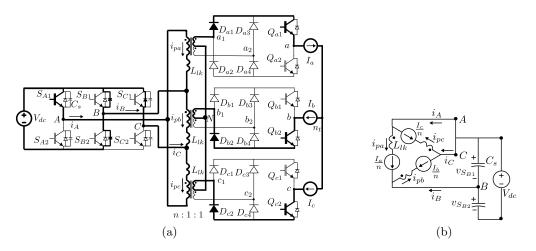

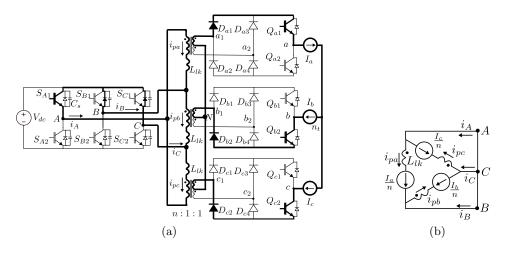

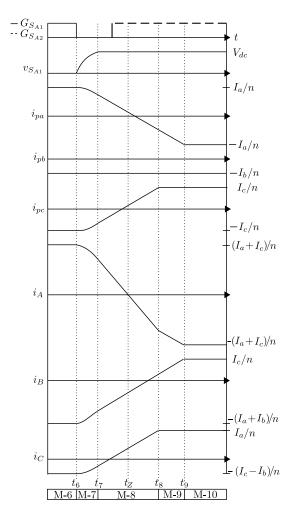

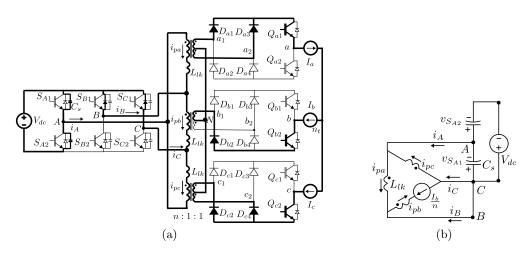

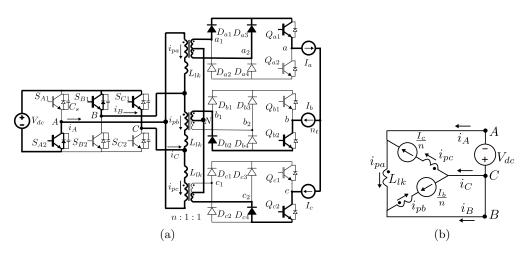

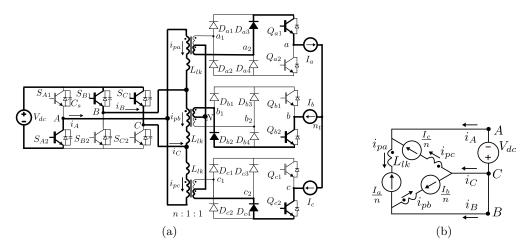

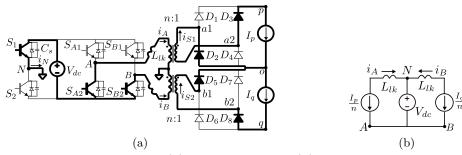

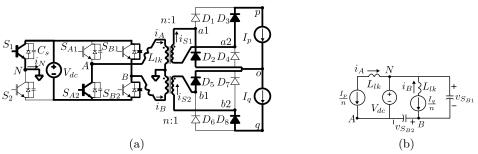

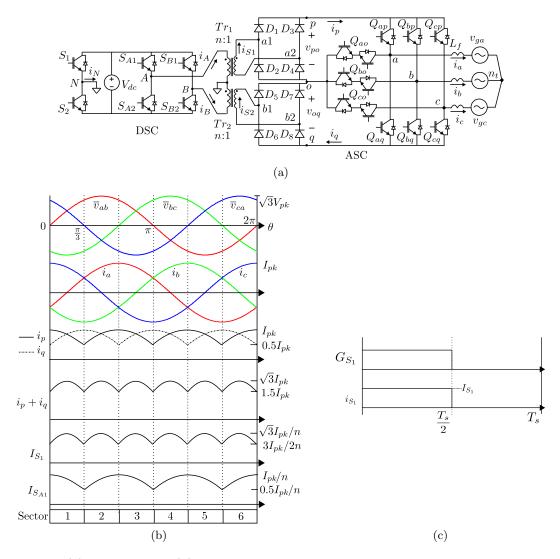

| 3 | Uni          | irectional HFL DC- $3\phi$ AC with 3 pulsating DC links: Topology-2 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| J | 3.1          | $117 \pm 100-3\phi$ AC with 5 pulsating DC links. Topology-2 45 introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

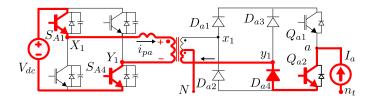

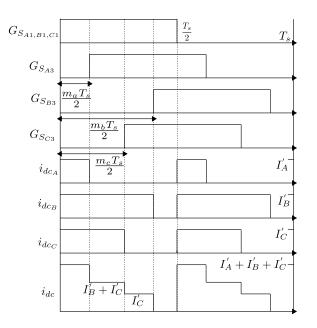

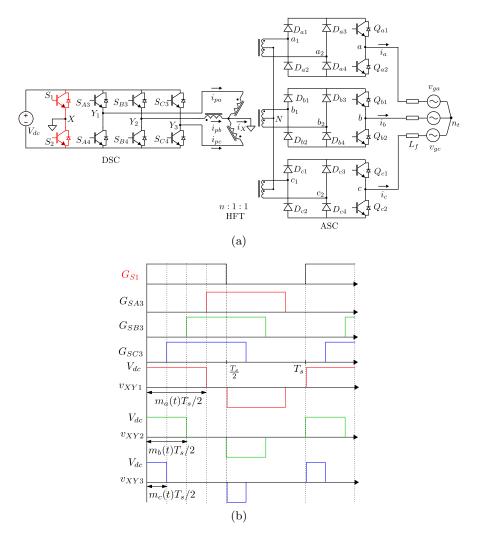

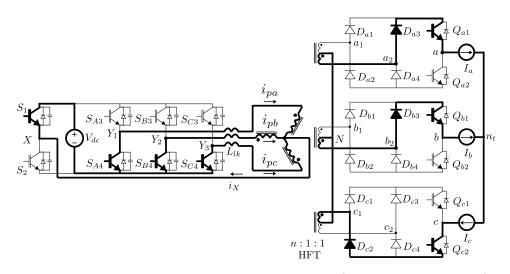

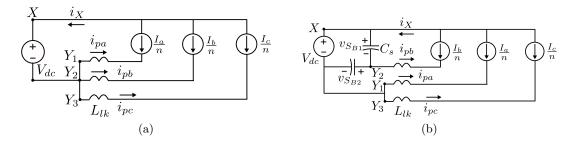

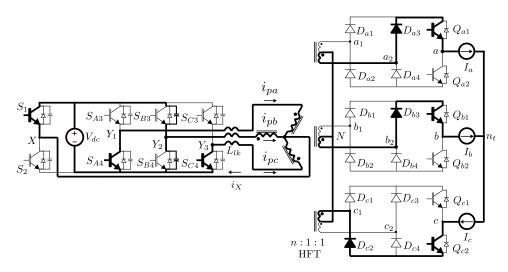

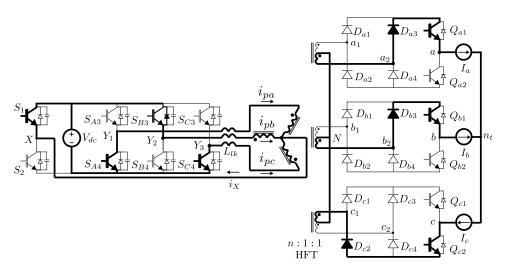

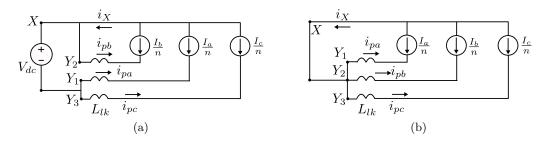

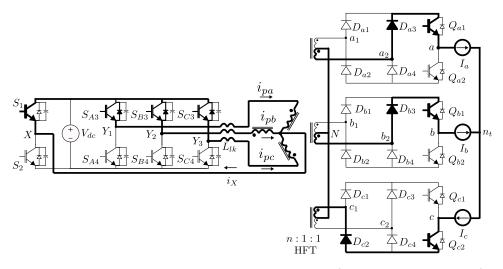

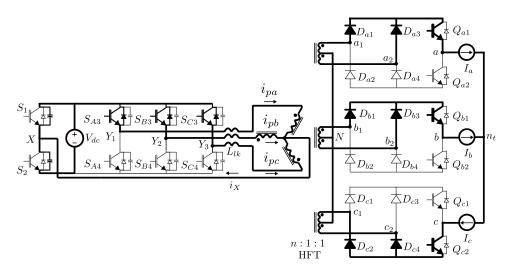

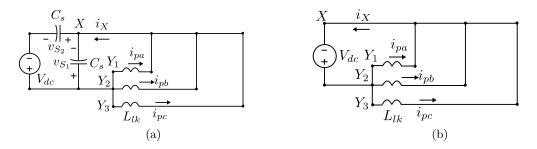

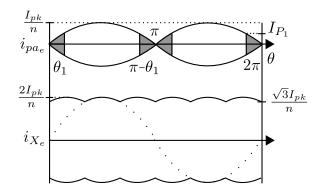

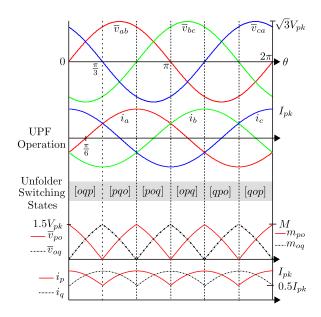

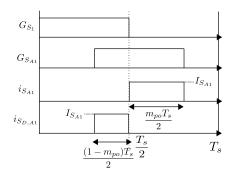

|   | $3.1 \\ 3.2$ | Inforduction       45         Fopology synthesis and modulation strategy       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

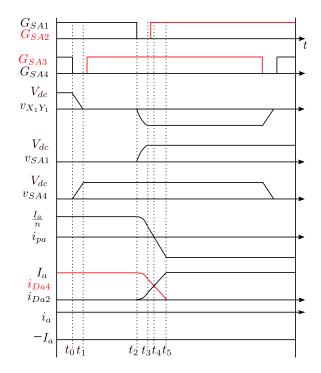

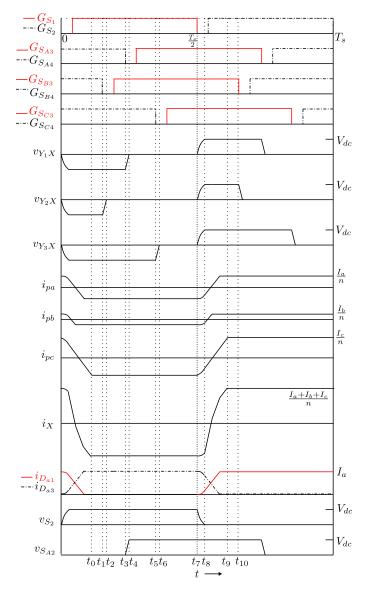

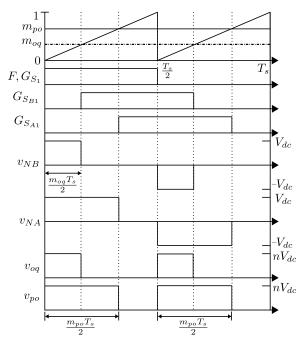

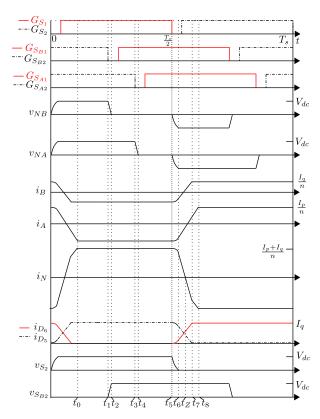

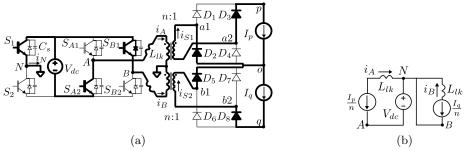

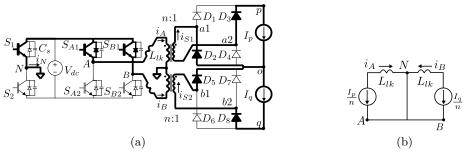

|   | 3.2          | Steady-state operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

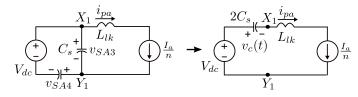

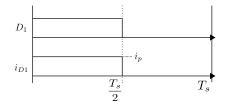

|   | 0.0          | B.3.1 Mode 1 $(t_0 < t < t_1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

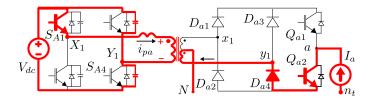

|   |              | $3.3.2  \text{Mode 1} \ (t_0 < t < t_1) \ \dots \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|   |              | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|   |              | $3.3.4  \text{Mode } 4.6  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|   |              | B.3.5       Mode 4-0 $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

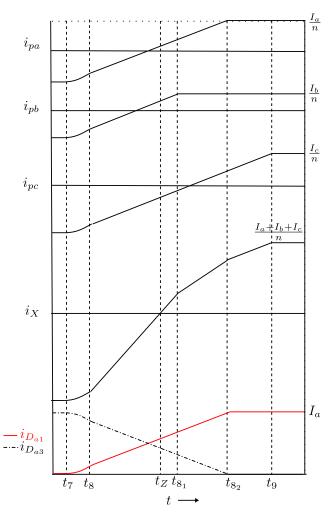

|   |              | <b>3.3.6</b> Mode 8 $(t_7 < t < t_8)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|   |              | $3.3.7  \text{Mode 9} \ (t_7 < t < t_8) \ \dots \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|   |              | $3.3.8  \text{Mode 9} \ (t_8 < t < t_9) \ \dots \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

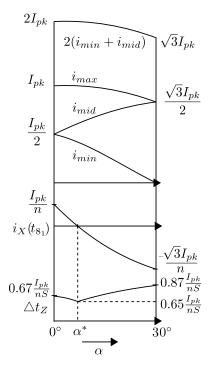

|   |              | B.3.9 Soft-switching condition of the reference leg $S_1 - S_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

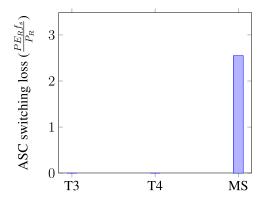

|   |              | 3.3.10 Comparison of soft-switching performance between topology 1 and 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

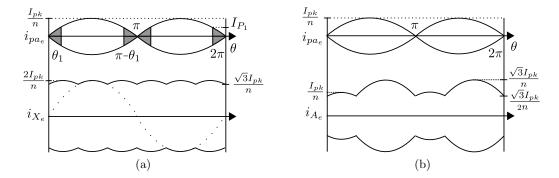

|   | 3.4          | Converter design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|   | <b>J</b> .1  | 3.4.1 Device blocking voltage and RMS currents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|   |              | B.4.2       Estimation of Converter Power Loss       60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |